計算機系統(tǒng)集成是計算機組成原理中的核心概念,它描述了計算機各硬件部件如何協(xié)同工作,構(gòu)成一個完整的、可運行的系統(tǒng)。理解系統(tǒng)集成對于掌握計算機的宏觀工作原理至關(guān)重要。

一、 系統(tǒng)集成的層次與核心部件

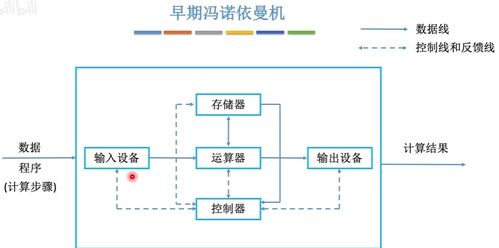

一個完整的計算機系統(tǒng)通常遵循經(jīng)典的馮·諾依曼體系結(jié)構(gòu),由五大功能部件集成而成:

1. 運算器(ALU): 執(zhí)行算術(shù)和邏輯運算的核心部件。

2. 控制器(CU): 計算機的“指揮中心”,從內(nèi)存中取出指令、譯碼并發(fā)出控制信號,協(xié)調(diào)各部件工作。運算器和控制器合稱為中央處理器(CPU)。

3. 存儲器(Memory): 用于存儲程序和數(shù)據(jù),包括高速緩存(Cache)、主存(內(nèi)存)和輔助存儲器(如硬盤)。

4. 輸入設備(Input Devices): 如鍵盤、鼠標,將外部信息轉(zhuǎn)換為機器可識別的數(shù)據(jù)。

5. 輸出設備(Output Devices): 如顯示器、打印機,將處理結(jié)果轉(zhuǎn)換為人可感知的形式。

這些部件通過系統(tǒng)總線(Bus)相互連接,進行數(shù)據(jù)和指令的傳輸。

二、 系統(tǒng)集成的關(guān)鍵:總線與互連

總線是集成各部件的信息高速公路,其性能直接影響系統(tǒng)整體效率。主要分為:

? 數(shù)據(jù)總線(Data Bus): 雙向傳輸數(shù)據(jù),寬度決定了一次可傳輸?shù)臄?shù)據(jù)量(如64位)。

? 地址總線(Address Bus): 單向(從CPU發(fā)出),用于指定內(nèi)存或I/O設備的地址,寬度決定了系統(tǒng)的尋址能力(如32位地址總線可尋址4GB空間)。

? 控制總線(Control Bus): 傳輸各種控制信號,如讀/寫、中斷請求、總線請求等。

現(xiàn)代計算機通常采用多總線結(jié)構(gòu)(如CPU內(nèi)部總線、系統(tǒng)總線、PCI總線等)來提高并行性和效率。

三、 指令執(zhí)行過程:系統(tǒng)集成的動態(tài)體現(xiàn)

計算機的工作過程,本質(zhì)上是“取指-執(zhí)行”周期的循環(huán),完美體現(xiàn)了各部件如何集成運作:

- 取指(Instruction Fetch): 控制器將程序計數(shù)器(PC)中的指令地址送至地址總線,通過控制總線發(fā)出“讀”命令。存儲器將該地址對應的指令經(jīng)數(shù)據(jù)總線送至CPU的指令寄存器(IR)。

- 譯碼(Instruction Decode): 控制器對IR中的指令進行譯碼,識別操作類型和操作數(shù)地址。

- 執(zhí)行(Execute): 根據(jù)譯碼結(jié)果,控制器發(fā)出微操作控制序列。例如,若是加法指令,則可能將數(shù)據(jù)從內(nèi)存取至寄存器,再由運算器完成加法,結(jié)果存回寄存器或內(nèi)存。

- 回寫與更新PC: 將結(jié)果寫入目標位置,并更新PC指向下一條指令地址,周而復始。

四、 層次化存儲系統(tǒng):性能與容量的集成權(quán)衡

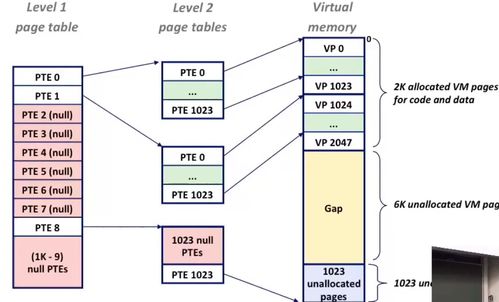

單一存儲器無法同時滿足速度快、容量大、成本低的要求。因此,系統(tǒng)采用層次化存儲結(jié)構(gòu)進行集成:

CPU寄存器 → Cache(SRAM) → 主存儲器(DRAM) → 輔助存儲器(磁盤/SSD)

從頂層到底層,訪問速度遞減,存儲容量遞增,單位成本遞減。通過硬件和操作系統(tǒng)的協(xié)同管理(如Cache映射、虛擬內(nèi)存),使得整個存儲系統(tǒng)在程序員看來像一個速度接近Cache、容量接近磁盤的統(tǒng)一整體,這是系統(tǒng)集成思想的杰出范例。

五、 輸入/輸出(I/O)系統(tǒng)集成

I/O設備與主機的集成方式主要有:

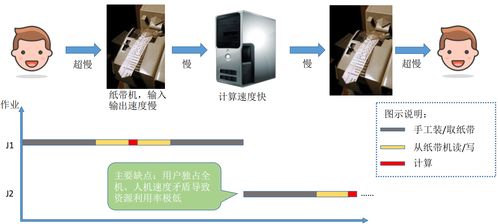

? 程序查詢方式: CPU主動輪詢I/O狀態(tài),效率低。

? 中斷方式: I/O完成后主動向CPU發(fā)出中斷請求,CPU暫停當前程序進行處理,提高了利用率。

? DMA(直接存儲器存取)方式: 由DMA控制器在I/O設備與內(nèi)存之間直接進行數(shù)據(jù)交換,傳輸完成后才通知CPU,極大解放了CPU。

這些方式體現(xiàn)了系統(tǒng)集成中“分工協(xié)作、提高效率”的設計哲學。

與考研要點

計算機系統(tǒng)集成的核心在于理解各部件功能、互連方式(總線)及協(xié)同工作機制(指令周期、存儲層次、I/O方式)。考研復習中,需重點掌握:

? 馮·諾依曼結(jié)構(gòu)的特點與工作流程。

? 總線的分類、特性和總線仲裁方式。

? 指令執(zhí)行各階段的數(shù)據(jù)流與控制流。

? Cache-主存-外存三級結(jié)構(gòu)的原理、映射方式及性能計算(命中率、平均訪問時間)。

? 程序中斷與DMA的工作機制、過程及比較。

掌握這些內(nèi)容,便能從整體上把握計算機是如何被集成并運行起來的,為后續(xù)深入學習處理器設計、并行計算等奠定堅實基礎(chǔ)。